## Dual-Channel 1206-8 ChipFET<sup>®</sup> Power MOSFET Recommended Pad Pattern and Thermal Performance

#### INTRODUCTION

New Vishay Siliconix ChipFETs in the leadless 1206-8 package feature the same outline as popular 1206-8 resistors and capacitors but provide all the performance of true power semiconductor devices. The 1206-8 ChipFET has the same footprint as the body of the LITTLE FOOT® TSOP-6, and can be thought of as a leadless TSOP-6 for purposes of visualizing board area, but its thermal performance bears comparison with the much larger SO-8.

This technical note discusses the dual ChipFET 1206-8 pin-out, package outline, pad patterns, evaluation board layout, and thermal performance.

#### **PIN-OUT**

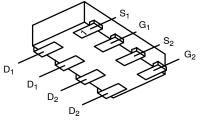

Figure 1 shows the pin-out description and Pin 1 identification for the dual-channel 1206-8 ChipFET device. The pin-out is similar to the TSOP-6 configuration, with two additional drain pins to enhance power dissipation and thus thermal performance. The legs of the device are very short, again helping to reduce the thermal path to the external heatsink/pcb and allowing a larger die to be fitted in the device if necessary.

Dual 1206-8 ChipFET

FIGURE 1.

For package dimensions see the 1206-8 ChipFET package outline drawing (http://www.vishay.com/doc?71151).

### **BASIC PAD PATTERNS**

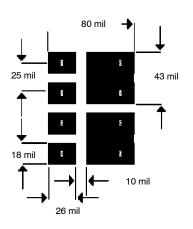

The basic pad layout with dimensions is shown in Application Note 826, *Recommended Minimum Pad Patterns With Outline Drawing Access for Vishay Siliconix MOSFETs*, (http://www.vishay.com/doc?72286). This is sufficient for low power dissipation MOSFET applications, but power semiconductor performance requires a greater copper pad area, particularly for the drain leads.

FIGURE 2. Footprint With Copper Spreading

The pad pattern with copper spreading shown in Figure 2 improves the thermal area of the drain connections (pins 5 and 6, pins 7 and 8) while remaining within the confines of the basic footprint. The drain copper area is 0.0019 sq. in. or 1.22 sq. mm. This will assist the power dissipation path away from the device (through the copper leadframe) and into the board and exterior chassis (if applicable) for the dual device. The addition of a further copper area and/or the addition of vias to other board layers will enhance the performance still further. An example of this method is implemented on the Vishay Siliconix Evaluation Board described in the next section (Figure 3).

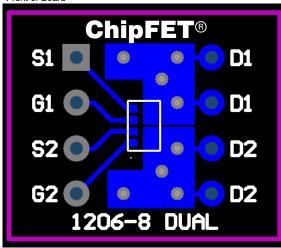

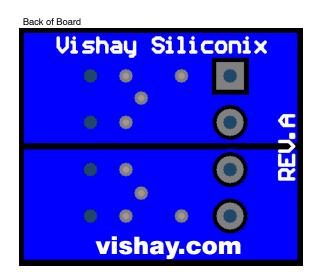

### THE VISHAY SILICONIX EVALUATION BOARD FOR THE DUAL 1206-8

The dual ChipFET 1206-08 evaluation board measures 0.6 in by 0.5 in. Its copper pad pattern consists of an increased pad area around each of the two drain leads on the top-side approximately 0.0246 sq. in. or 15.87 sq. mm—and vias added through to the underside of the board, again with a maximized copper pad area of approximately the board-size dimensions, split into two for each of the drains. The outer package outline is for the 8-pin DIP, which will allow test sockets to be used to assist in testing.

The thermal performance of the 1206-8 on this board has been measured with the results following on the next page. The testing included comparison with the minimum recommended footprint on the evaluation board-size pcb and the industry standard one-inch square FR4 pcb with copper on both sides of the board.

## AN812 Vishay Siliconix

Front of Board

#### THERMAL PERFORMANCE

## Junction-to-Foot Thermal Resistance (the Package Performance)

Thermal performance for the 1206-8 ChipFET measured as junction-to-foot thermal resistance is 30°C/W typical, 40°C/W maximum for the dual device. The "foot" is the drain lead of the device as it connects with the body. This is identical to the dual SO-8 package  $R_{\Theta jf}$  performance, a feat made possible by shortening the leads to the point where they become only a small part of the total footprint area.

# Junction-to-Ambient Thermal Resistance (dependent on pcb size)

The typical  $R_{\Theta ja}$  for the dual-channel 1206-8 ChipFET is 90°C/W steady state, identical to the SO-8. Maximum ratings are 110°C/W for both the 1206-8 and the SO-8. Both packages have comparable thermal performance on the 1" square pcb footprint with the 1206-8 dual package having a quarter of the body area, a significant factor when considering board area.

#### Testing

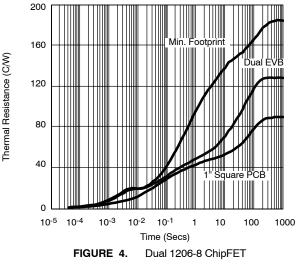

To aid comparison further, Figure 4 illustrates ChipFET 1206-8 dual thermal performance on two different board sizes and three different pad patterns. The results display the thermal performance out to steady state and produce a graphic account on how an increased copper pad area for the drain connections can enhance thermal performance. The measured steady state values of  $R_{\Theta\,j\,a}$  for the Dual 1206-8 ChipFET are :

| 1) Minimum recommended pad pattern (see<br>Figure 2) on the evaluation board size of<br>0.5 in x 0.6 in. | 185°C/W |

|----------------------------------------------------------------------------------------------------------|---------|

| 2) The evaluation board with the pad pattern described on Figure 3.                                      | 128°C/W |

| 3) Industry standard 1" square pcb with maximum copper both sides.                                       | 90°C/W  |

The results show that a major reduction can be made in the thermal resistance by increasing the copper drain area. In this example, a  $57^{\circ}$  C/W reduction was achieved without having to increase the size of the board. If increasing board size is an option, a further  $38^{\circ}$  C/W reduction was obtained by maximizing the copper from the drain on the larger 1" square PCB.

#### SUMMARY

The thermal results for the dual-channel 1206-8 ChipFET package display identical power dissipation performance to the SO-8 with a footprint reduction of 80%. Careful design of the package has allowed for this performance to be achieved. The short leads allow the die size to be maximized and thermal resistance to be reduced within the confines of the TSOP-6 body size.

#### **ASSOCIATED DOCUMENT**

1206-8 ChipFET Single Thermal performance, AN811, (http://www.vishay.com/doc?71126).